■ 반도체 패키징 기술은 2차원(2D)에서 3차원(3D)으로 반도체 패키지의 밀도 향상과 성능 향상이 한층 더 진행되고 있다. 과거, 고성능 컴퓨팅용 대규모 프로세서는 CPU 회로와 입출력 회로를 복수의 미니 다이(칩렛)로 분할하여 미세 배선 회로의 인터포저(중간 기판)에 탑재함으로써, 실장 밀도, 동작 주파수 등 신호 전송 대역의 향상을 실현해 왔다.

AMD가 ECTC 2024에서 발표한 논문에서 (논문 번호 19.6)당초, 미니다이는 중간 기판 위에 나란히 탑재하고 있었다. 기존의 패키지 기판과 다른 것은, 인터포저에서는 미니다이의 간격을 크게 채울 수 있다는 것이다. 동시에 미니다이의 입출력 패드 간격도 채울 수 있다. 모두 인터포저에서는 기존의 패키지 기판에 비해 미세한 배선을 형성할 수 있는 것이 크게 기여하고 있다. 미니다이의 입출력 패드 간격이 막히면, 단위 면적당 전송 채널 수를 늘릴 수 있다. 고밀도화와 고성능화를 모두 실현할 수 있다. 이것이 '2.5차원(2.5D) 패키징'이라고 불리는 선진 패키징 기술이다. 또한 종래의 패키징 기술은 구별을 위해 '2차원(2D) 패키징'이라고 불리게 되었다. 다음으로 밀도와 성능을 더욱 향상시키기 위해, 미니다이를 가로로 늘어놓는 것이 아니라, 세로로 늘어놓는, 즉 적층하는 것을 생각할 수 있었다. 패키지 기판 위에 여러 개의 미니다이를 적층하면, 실장 면적을 크게 줄일 수 있다. 미니다이 사이를 연결하는 거리는, 나란히 늘어놓은 경우에 비해 크게 줄어든다. 이것이 '3차원(3D) 패키징'이라고 불리는 어드밴스드 패키징 기술이다.

■ 3D와 2.5D를 조합하여 3.5D로 패키지의 집적밀도와 동작 성능을 더욱 높이는 것이, '3.5차원(3.5D) 패키징'이라고 불리는 기술이다. 3D 패키지와 2.5D 패키지를 조합한 패키지가 된다. 2024년 5월 28일~31일에 미국 콜로라도주 덴버에서 개최된 반도체 패키징 기술에 관한 세계 최대의 국제 학회 'ECTC 2024(The 2024 IEEE 74th Electronic Co mponents and Technology Conference)'에서는, AMD와 인텔이 각각, 3.5D 패키징의 개발 성과를 발표했다. AMD는 2023년 12월에 발표한 최신 GPU 제품 'MI300 시리즈'에 3.5D 패키징 기술을 채용했다. 2.5D의 패키징 기술은 실리콘 인터포저와 입출력 다이(IOD), HBM 모듈의 접속에 도입했다. 즉 인터포저 위에 IOD와 HBM 모듈을 마이크로 범프에 의해 연결하고 있다. 인터포저의 면적은 3,000평방mm(정사각형 환산으로 54.77mm각)로 상당히 크다. 노광 영역(레티클)의 약 3.6배에 해당한다. 3D 패키징 기술은, IOD와 CPU 다이(CCD) 혹은 GPU 다이(XCD)의 3차원 적층(3D Stack)에 도입했다. IOD에 형성된 실리콘 관통 비아(TSV) 전극과 CCD 혹은 XCD의 표면 전극을 하이브리드 접합에 의해 적층/접속하고 있다. 또한 MI300시리즈에는 APU제품의 'MI300A'와 GPU제품의 'MI300X'가 있지만, 패키징 기술은 거의 변하지 않는다.

■ 인텔은 3.5D용으로 양산 수준의 3μm 피치 HBI 기술을 개발 인텔도, 3D 패키지와 2.5D 패키지를 조합한 3.5D 패키징 기술을 개발하고 있다.

그 한쪽 끝을, ECTC 2024에서 공표했다(논문 번호 2.3). 공표한 패키지 단면의 예는, 패키지 기판에 실리콘의 작은 조각('EMIB:embedded multi-die interconnect bridges'과 인텔은 호칭)을 묻어 미니 다이 간의 배 선 피치를 좁히는 동시에 실리콘 다이 사이의 거리를 줄이는 2.5D 패키징 기술과, 미니 다이를 세로로 적층하는 3D 패키징 기술을 조합한 것.

미니 다이의 적층 접속에는 마이크로 범프 혹은 하이브리드 접합(HB:hybrid bonding)을 구사한다.

강연에서는, 3D 패키징의 요소 기술인 HBI(Hybrid Bonding Interconnect)의 연구 성과를 말했다.

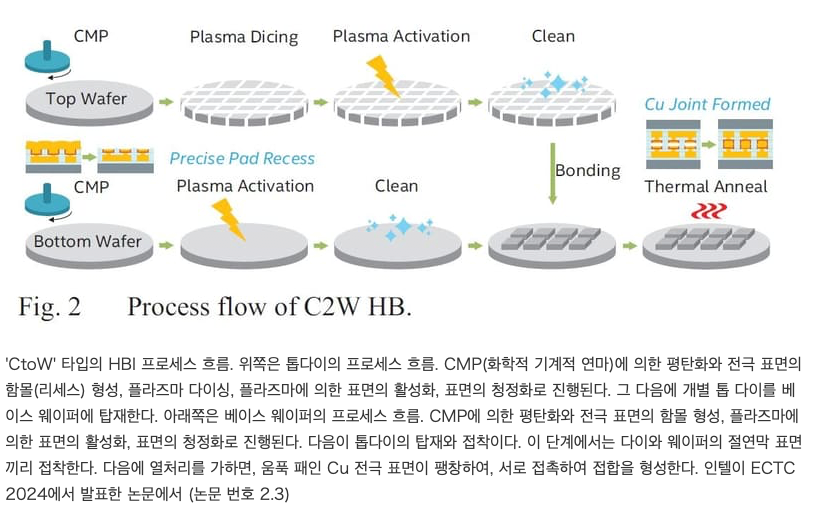

칩과 웨이퍼를 연결하는 'CtoW(C2W)' 타입의 HBI 기술을 개량하여, 양산 가능한 수준에서 접속 피치가 3μm로 좁은 HBI 기술을 개발해 보였다.

개발에 있어서는, 테스트용 미니 다이와 미니 웨이퍼를 작성하고, 미니 다이와 미니 웨이퍼 사이에서 하이브리드 접합을 실시했다. 미니다이의 크기는 6.2×7.7mm이다. 미니 웨이퍼에는 가로 방향으로 4장, 세로 방향으로 2장의 톱 다이를 탑재할 수 있다. 하이브리드 접합에 의해 접속부는 데이지 체인 모양이 된다. 데이지 체인을 만드는 것은, 수많은 접합을 연결함으로써, 전체의 전기적 특성을 측정하기 쉽도록 하기 위해서다.

■ 25,600의 데이지 체인으로 균일한 저항치를 확인 톱다이는 64개의 데이지 체인을 만들어 놨다.

400장의 톱다이로 4단자법에 의해 HBI 후의 전기 저항을 측정했다. 총 25,600개의 데이지 체인에 비해, 저항의 변화는 거의 없었다. 또한 정렬 오차는 400장의 톱다이에 대해 0.5μm 이하에 그쳤다. 신뢰성 시험도 실시했다. uHAST(unbiased Highly Accelerated Stress Test), 온도 사이클(TC:Thermal Cycle) 시험, 고온 방치(HTS:High Temperature Storage) 시험이다. uHAST의 시험 조건은 110℃, 85%RH, 275시간 동안 78개의 샘플이 모두 양품인 채로 있었다. 온도 사이클 시험의 조건은 저온 쪽이 -55℃, 고온 쪽이 125℃, 15분씩 750사이클이다. 80개의 샘플은 모두 시험을 통과했다. 고온 방치 시험의 조건은 165℃, 336시간으로, 80개의 샘플에서 불량품은 전혀 나오지 않았다.

AMD와 인텔의 발표에서 알 수 있는 것은, 3D 패키징에서는 하이브리드 접합에 의한 접속을 중시하고 있다는 것이다. 실리콘 다이끼리의 접속 밀도를 비약적으로 높이는 기술로는, HBI가 가장 유력시되고 있다. 한편으로 기술적인 어려움도 상당한 것이다. 이 때문에 ECTC 2024에서는, 하이브리드 접합에 관한 발표가 매우 활발했다. 앞으로의 발전을 강력히 기대하고 싶다.

출처 : PC watch

'반도체' 카테고리의 다른 글

| TSMC는 EUV에 123억 달러 이상을 투자하여 2nm 생산을 발전 (1) | 2024.06.29 |

|---|---|

| 마이크론 GDDR7 메모리 발표, 게임 성능 30% 향상 (2) | 2024.06.08 |

| 반도체 미세화 패터닝도 ai가 담당. (0) | 2024.06.01 |

| 인텔 파운드리 (2) | 2024.05.31 |

| 인텔의 도약 및 경쟁회사 칩 TEM 단면도 (0) | 2024.05.29 |